Projekt AudioSigLib

Ziel

- Hardware & Software Platform zur Audio Signal Verarbeitung

- Aufbau einer Bibliothek mit IP-Blöcken zur Audio Signal Verarbeitung

- HLS testen und Resultate mit HDL vergleichen

Motivation

- Echtzeitverarbeitung

- Kombination aus Hard- und Software

- Keine CPU-Zeit für die Signalverarbeitung

- Flexibel und Modular - Wiederverwendbarkeit

Übersicht

Hardware - Digilent Zybo-Z7

- Xilinx SoC

- FPGA und ARM Core

Xilinx Zynq

Vorwissen

| Xilinx Vivado | HDL Design | Xilinx SoC | Linux Treiber | GIT | AXI4 | |

|---|---|---|---|---|---|---|

| Elias | n | j | n | j | j | n |

| Daniel | n | j | n | j | j | n |

| Martin | n | n | n | n | j | n |

| Franz | j | j | n | n | j | j |

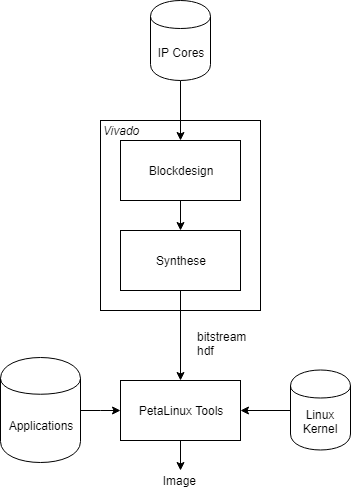

Tools

- Xilinx Vivado & SDK

- Sigasi Studio

- Modelsim - Intel FPGA Starter Edition

- Xilinx PetaLinux Tools

- GIT - Gitlab

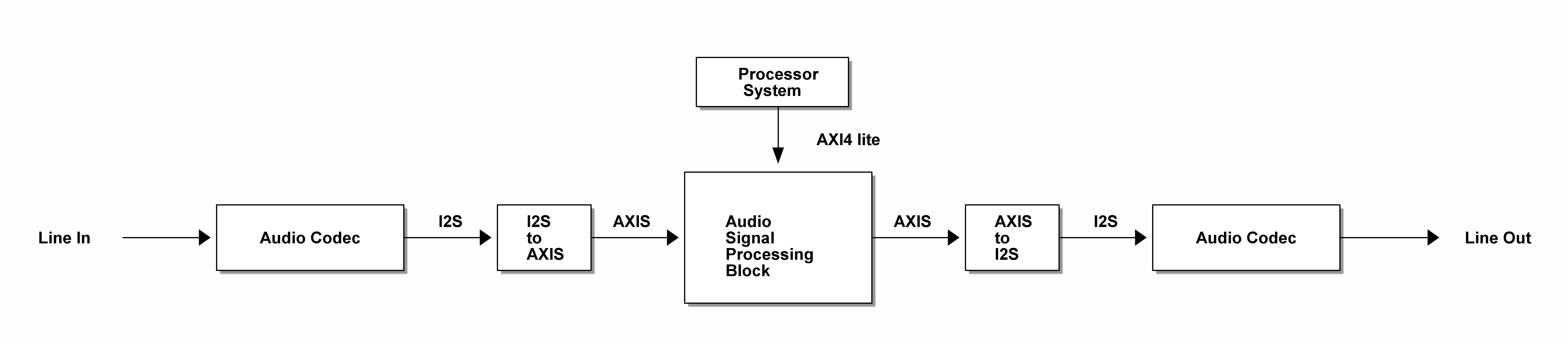

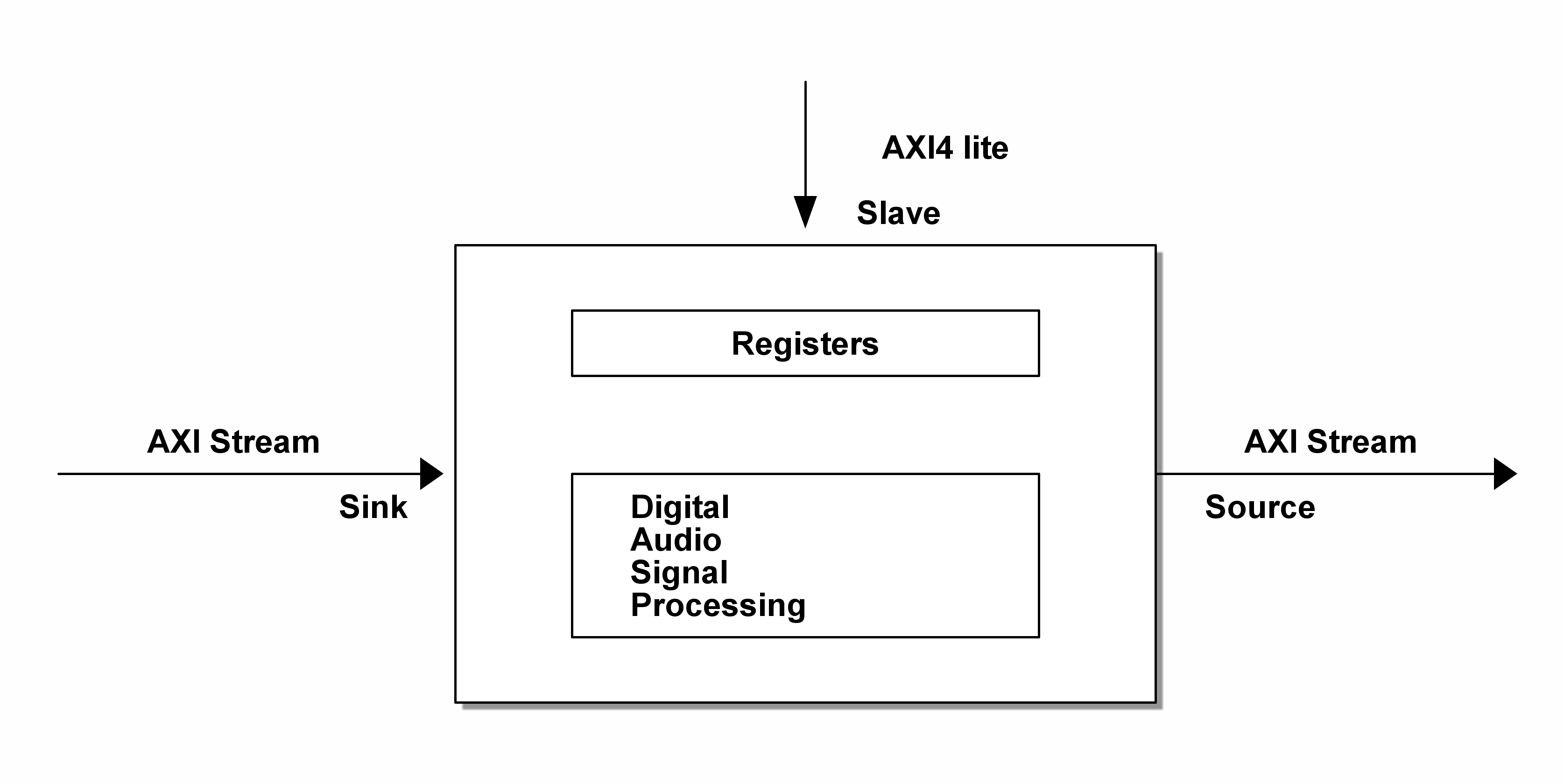

Umsetzung

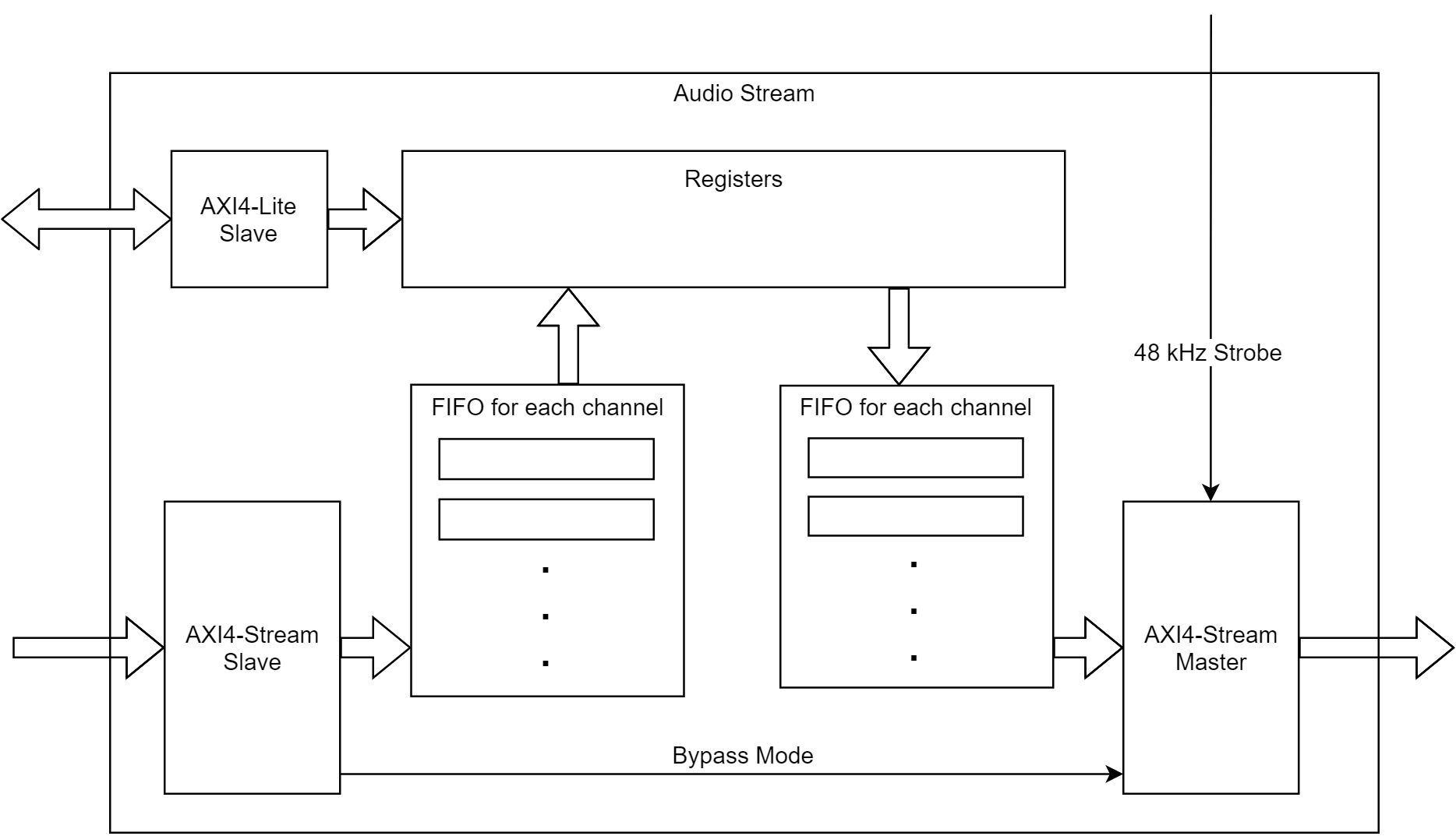

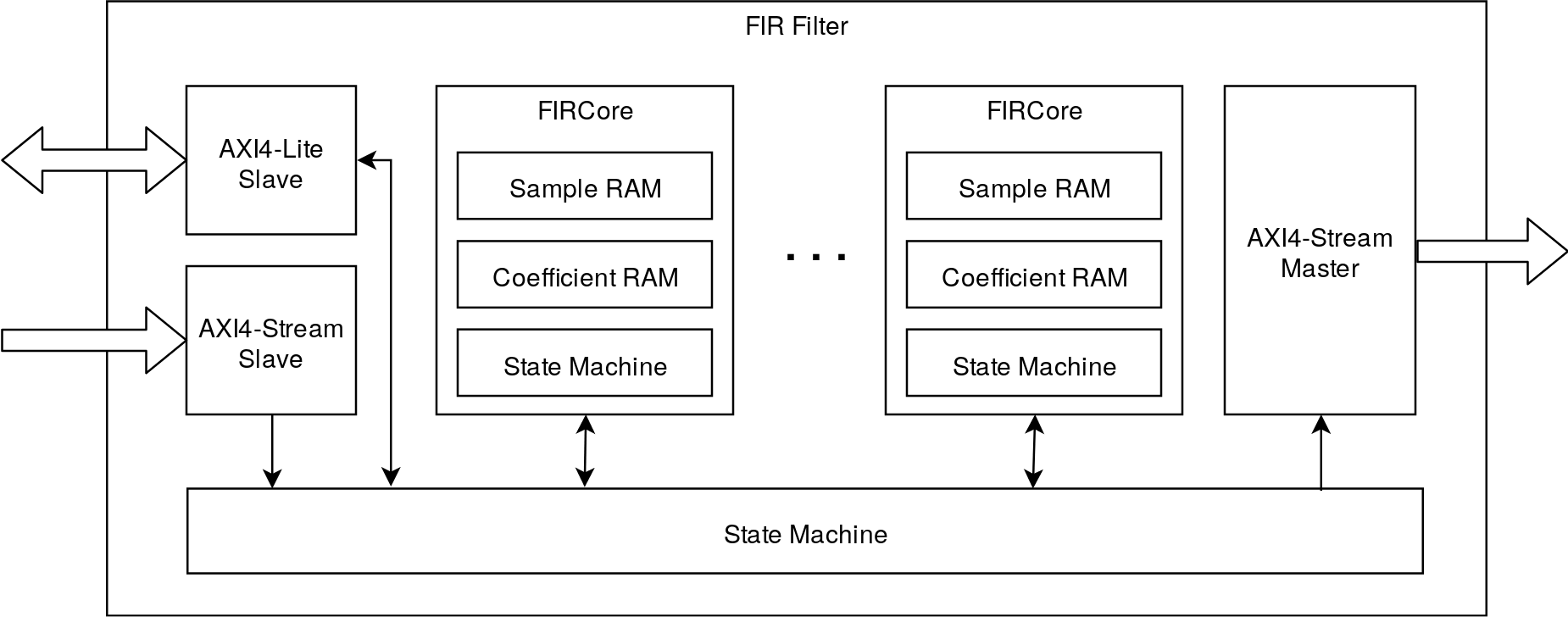

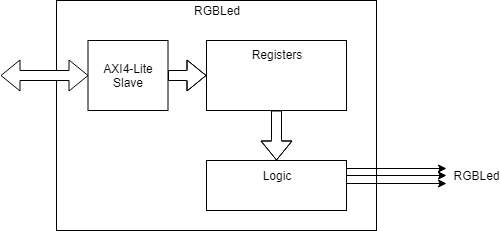

AXI4-lite - Memory Mapped

Register Map

| Address | Register | Description |

|---|---|---|

| 0x00 | ID | library component identifier |

| 0x04 | Verison | library component version number |

| 0x08 | Position | position inside the processing chain |

| 0x0C - … | component specific registers | |

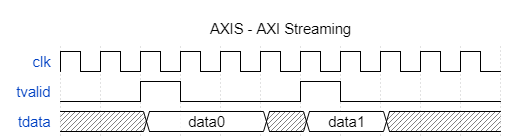

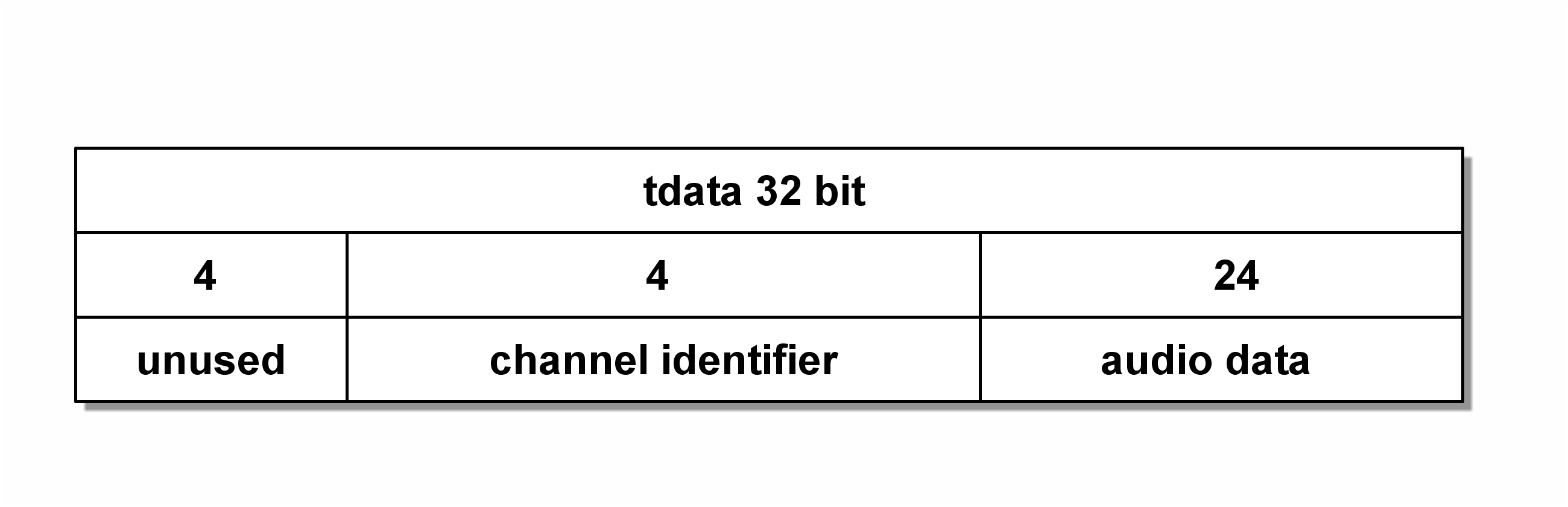

AXI4 Stream - Daten

Daten Paket

Design Flow

Resultat

Status

- Funktionale Platform (HW & SW)

- Konzept bewiesen

- Erste Blöcke fertig und getestet

- Git Repo mit Wiki und Anleitung!

AudioStream

FIR Filter

RGB LED Controller

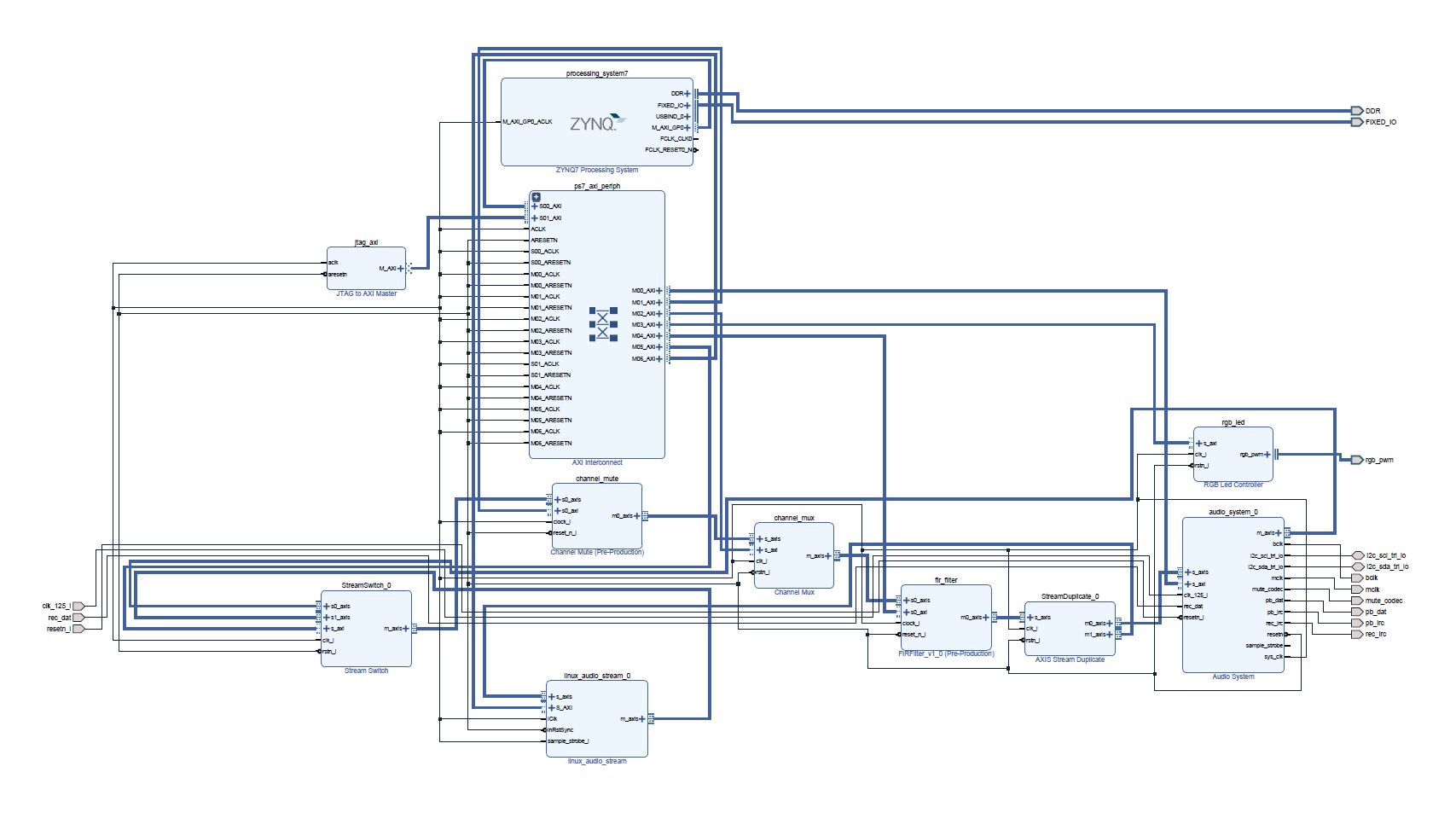

Gesamtsystem

Schwierigkeiten

Xilinx Vivado

- Versionskonflikte (TCL Befehle, IP Cores)

- GIT & Vivado

- Instabil

- Datein werden kopiert, Änderungen teilweise nicht übernommen

- Relative und Absolute Pfade, zB: ../../../../../../C:/Users/Franz/FH/AudioSigLib/ip/FIR/hdl/

- PetaLinux Tools verwendet ältere Vivado Version

- Funktion vom OS abhängig (Simulator)

- Fehlermeldungen werden nicht gelöscht - selber löschen

Ausfall eines Teammitglieds

- Folge: Wegfallen der HLS

Verifikation

- Aufwendig

IIR Filter Design

- Skalierung der Filterkoeffizenten

PetaLinux Tools

- sehr Aufwendig

- neuer bitstream erfordert neues Image

Generisches Design

- sehr Aufwendig

Verbesserungen

- Gleiche Vivado Version auf allen PCs

- (Gleiches OS = Virtuelle Maschiene)

- Besserer Workflow mit Git und Vivado

- Eigenes Testbed um IP Cores und Blockdesign bei der Implementierung zu vermeiden

- Viel Zeit für Vivado einplanen…

Team

Projekt Team

- Geissler Elias, BSc

- Klepatsch Daniel, BSc

- Schram Martin, BSc

- Steinbacher Franz, BSc

Projekt Betreuer

- FH-Prof. Dipl-Ing. Dr. Markus Pfaff

University of Applied Sciences Upper Austria

Campus Hagenberg

Department Embedded Systems Design